如何通過Prodigy I3C協議調試簡化DDR5內存設計

- 時間:2025-10-11作者:深圳市歐奧電子科技有限公司瀏覽:84

深圳市歐奧電子科技有限公司專注于芯片研發測試設備,芯片研發測試解決方案,高難度焊接和信號抓取分析服務等

詞條

詞條說明

使用 PGY-PCIeLP-SBA 對 PCIe 接口進行邊帶信號分析

芯片供應商需要驗證 DUT 不同狀態下邊帶信號的電氣時序測量,并查看長期一致性。為了滿足這一要求,Prodigy Technovations 開發了?PCIe邊帶信號分析儀。它監控這些信號并提供多周期運行中測量的統計信息,以確保穩定可靠的運行。PGY-PCIeLP-SBA 包括 discovery 系列邏輯分析儀(掌上大小),帶有用于 REFCLK 的 PCIe 邊帶信號分析的定制邏輯、

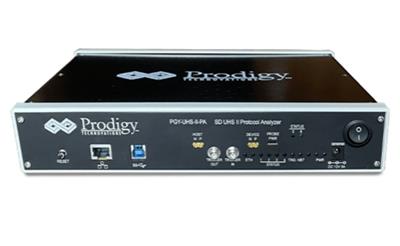

Prodigy Technovations宣布推出的 PCIeGen3/4 協議分析儀

Prodigy Technovations Pvt. Ltd 是一家總部位于班加羅爾的公司,推出了支持 2.5、5.0 、8.0 和 16GT/S 速度的 PGY-PCIeGen3/4-PA PCIe 協議分析儀。PCIeGen3/4 協議分析儀可用于開發和驗證 M.2、U.2 和嵌入式接口的 PCIe 接口。移動、汽車和 5G 網絡的工程師使用該產品來調試 PCIe 中的協議層設計問題。PGY-

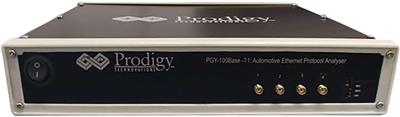

Prodigy 宣布推出世界上臺經過測試量產的UFS4.0 協議分析儀

總部位于班加羅爾的?Prodigy Technovations Pvt. Ltd 推出了其?PGY-UFS4.0-PA?M-PHYSM、UniPro? 和 UFS4.0 協議分析儀,用于開發下一代閃存 UFS 4.0,每通道接口 23.2 Gbps,用于 5G、移動、汽車、物聯網、AR/VR 應用。PGY-UFS4.0-PA?使設計和測試工程師能夠根據其規格

PGY-I2C/SPI-EX-PD 如何解決 I2C 通信中的時鐘拉伸問題

時鐘拉伸是 I2C 協議中從設備暫停通信的機制,但調試中常因時序不匹配導致數據丟失。PGY-I2C/SPI-EX-PD 通過靈活配置時鐘拉伸時間、可視化波形分析及精確時序測量,有效解決此類問題。在 I2C 通信中,若從設備處理速度較慢,需通過時鐘拉伸(拉低 SCL 線)延長數據準備時間。PGY-I2C/SPI-EX-PD 的解決方案包括:l自定義時序配置:工程師可在 ACK/NACK 階段或數據傳

聯系方式 聯系我時,請告知來自八方資源網!

公司名: 深圳市歐奧電子科技有限公司

聯系人: 鄭陽燕

電 話: 19926571623

手 機: 18588455974

微 信: 18588455974

地 址: 廣東深圳龍華區昌盛科技大廈503

郵 編:

相關推薦

相關閱讀

1、本信息由八方資源網用戶發布,八方資源網不介入任何交易過程,請自行甄別其真實性及合法性;

2、跟進信息之前,請仔細核驗對方資質,所有預付定金或付款至個人賬戶的行為,均存在詐騙風險,請提高警惕!

- 聯系方式

- 相關企業

- 重慶萊奧儀器有限公司

- 青島艾普歐盛電子科技有限公司

- 西安固泰傳感器有限公司

- 長沙富蘭德實驗分析儀器有限公司

- 濟南恒瑞金試驗機有限公司

- 南京邁捷克科技有限公司

- 西安西儀壓力儀表有限公司

- 貝斯特(亞洲)實業有限公司

- 鶴壁市藍博儀器儀表有限公司

- 商家產品系列

- 產品推薦

- 資訊推薦